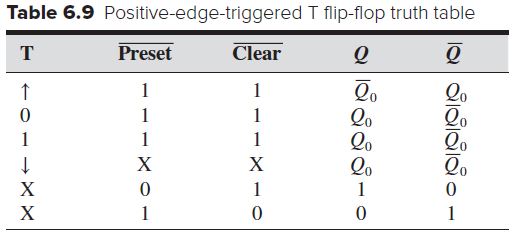

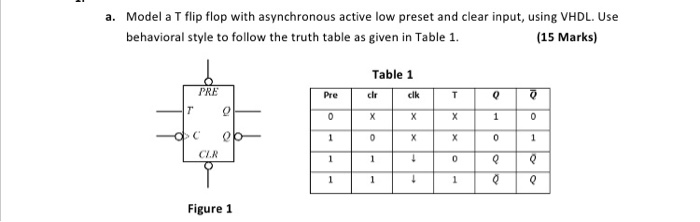

T Flip Flop Truth Table With Preset And Clear

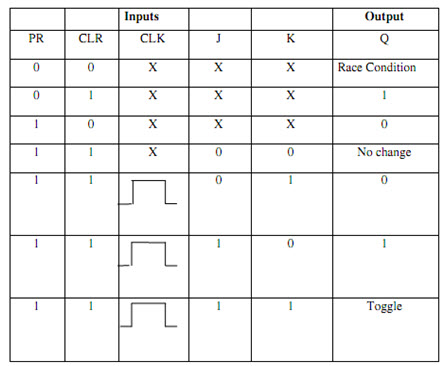

But even after correcting them in the back of my mind i think that the given truth table is not correct for the set and preset conditions for the given circuit.

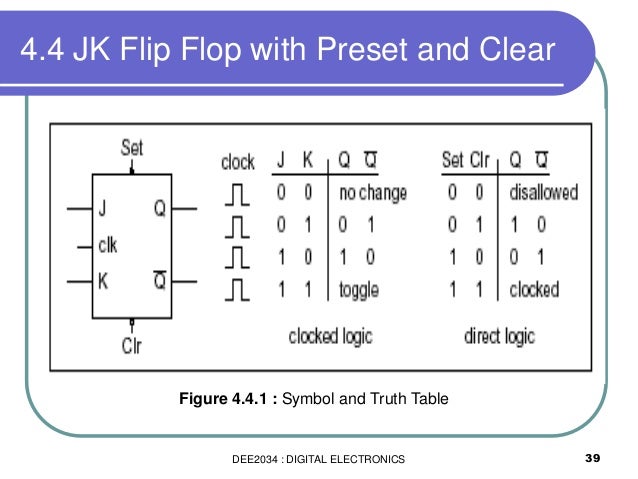

T flip flop truth table with preset and clear. Similarly a high signal to preset pin will make the q output to set that is 1. A high signal to clear pin will make the q output to reset that is 0. Jk flip flop preset and clear function. The name t flip flop is termed from the nature.

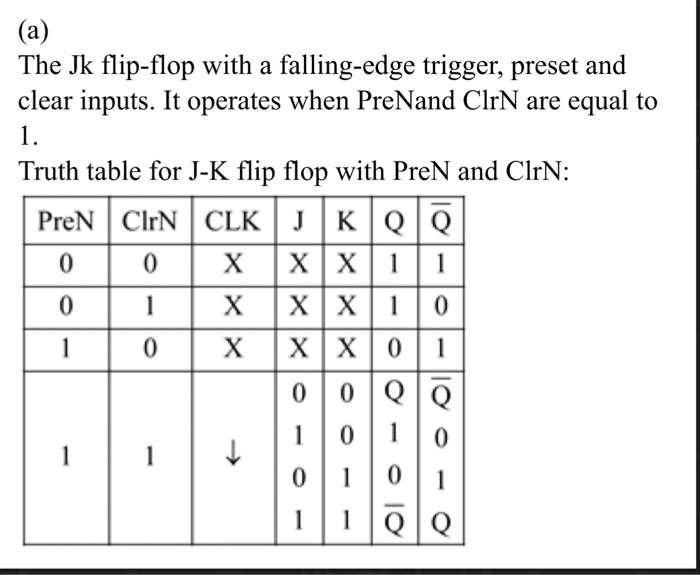

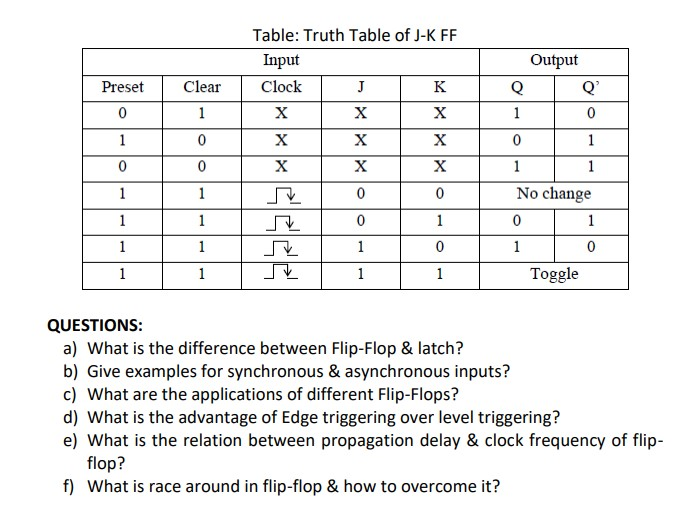

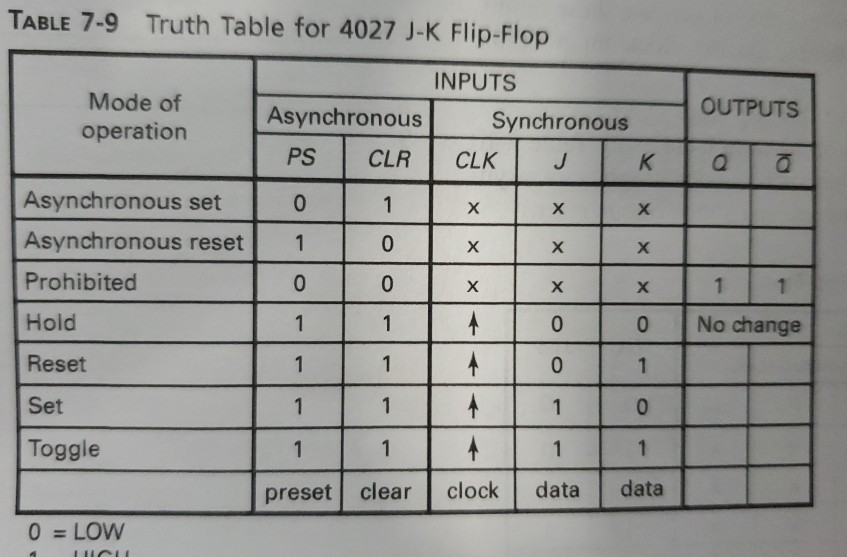

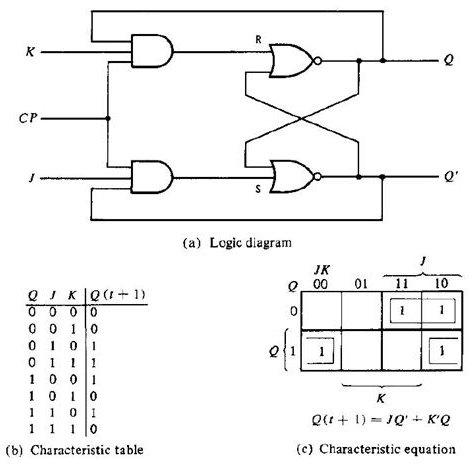

On the other hand if q 1 the lower nand gate is enabled and flip flop will be reset and hence q will be 0. In other words when j and k are both high the clock pulses cause the jk flip flop to toggle. Truth table characteristic table and excitation table for jk flip flop duration. See the j k and clock inputs with an x.

Truth table for jk flip flop is shown in table 8. The truth table of a t flip flop is shown below. If the output q 0 then the upper nand is in enable state and lower nand gate is in disable condition. Truth table of t flip flop.

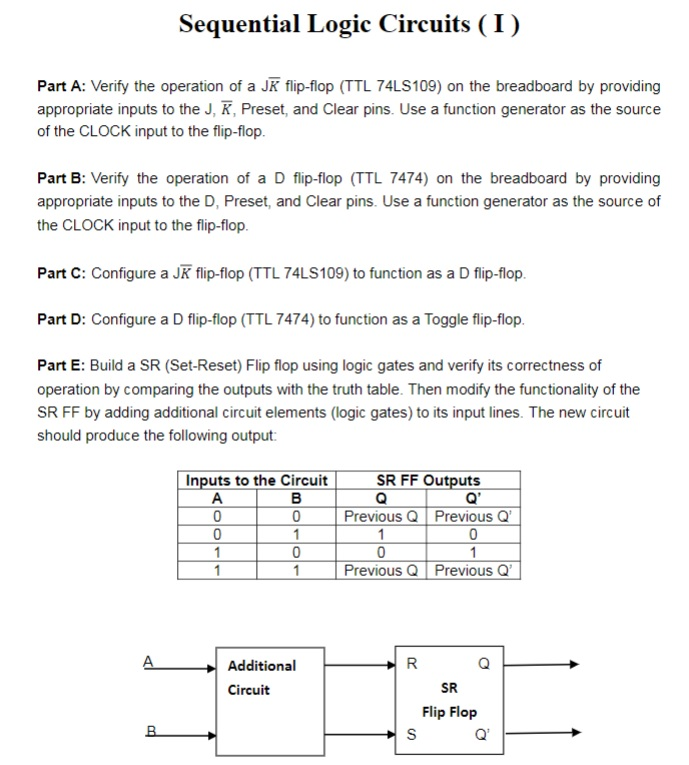

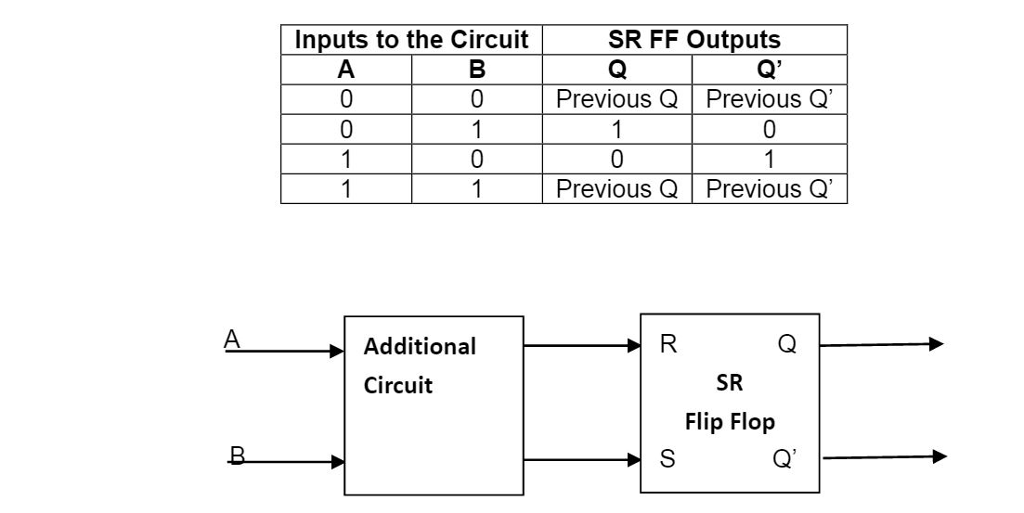

I think that for the circuit shown overline pre 0 and overline. Sr flip flop sr flip flop is the simplest type of flip flops. Rs flip flop reset set d flip flop data jk flip flop jack kilby t flip flop toggle out of the above types only jk and d flip flops are available in the integrated ic form and also used widely in most of the applications. Jk flip flop truth table.

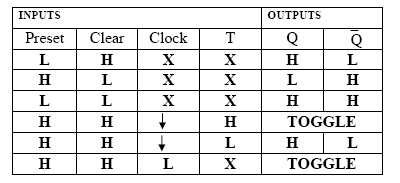

D flip flop has another two inputs namely preset and clear. T flip flop. Here in this article we will discuss about t flip flop. It stands for set reset flip flop.

It is a clocked flip flop. Construction of sr flip flop there are following two methods for constructing a sr flip flop by using nor latch. As mentioned earlier t flip flop is an edge triggered device. This will set the flip flop and hence q will be 1.

For example consider a t flip flop made of nand sr latch as shown below. The preset and clear input are active low because there are an inverting bubble at that input lead on the block symbol just like the negative edge trigger clock inputs. In this article we will discuss about sr flip flop. Hence the name itself explain the description of the pins.

When the preset input is activated the flip flop will be reset q 0 not q 1 regardless of any of the synchronous inputs or the clock.